# S1D13A04 LCD/USB Companion Chip

# **Hardware Functional Specification**

**Document Number: X37A-A-001-07**

Status: Revision 7.5

Issue Date: 2008/12/18

© SEIKO EPSON CORPORATION 2001 - 2008. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners.

# **Table of Contents**

| 1 | Introduction                                         |

|---|------------------------------------------------------|

|   | 1.1 Scope                                            |

|   | 1.2 Overview Description                             |

| 2 | Features                                             |

|   | 2.1 Integrated Frame Buffer                          |

|   | 2.2 CPU Interface                                    |

|   | 2.3 Display Support                                  |

|   | 2.4 Display Modes                                    |

|   | 2.5 Display Features                                 |

|   | 2.6 Clock Source                                     |

|   | 2.7 USB Device                                       |

|   | 2.8 2D Acceleration                                  |

|   | 2.9 Miscellaneous                                    |

| 3 | Typical System Implementation Diagrams               |

|   | 3.1 Typical System Diagrams                          |

|   | 3.2 USB Interface                                    |

| 4 | Pins                                                 |

|   | 4.1 Pinout Diagram - PFBGA - 121-pin                 |

|   | 4.2 Pinout Diagram - TQFP15 - 128-pin                |

|   | 4.3 Pin Descriptions                                 |

|   | 4.3.1 Host Interface                                 |

|   | 4.3.2 LCD Interface                                  |

|   | 4.3.3 Clock Input                                    |

|   | 4.3.4 Miscellaneous                                  |

|   | 4.3.5 Power And Ground                               |

|   | 4.4 Summary of Configuration Options                 |

|   | 4.5 Host Bus Interface Pin Mapping                   |

|   | 4.6 LCD Interface Pin Mapping                        |

| 5 | D.C. Characteristics                                 |

| 6 | A.C. Characteristics                                 |

|   | 6.1 Clock Timing                                     |

|   | 6.1.1 Input Clocks                                   |

|   | 6.1.2 Internal Clocks                                |

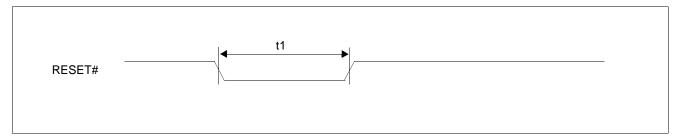

|   | 6.2 RESET# Timing                                    |

|   | 6.3 CPU Interface Timing                             |

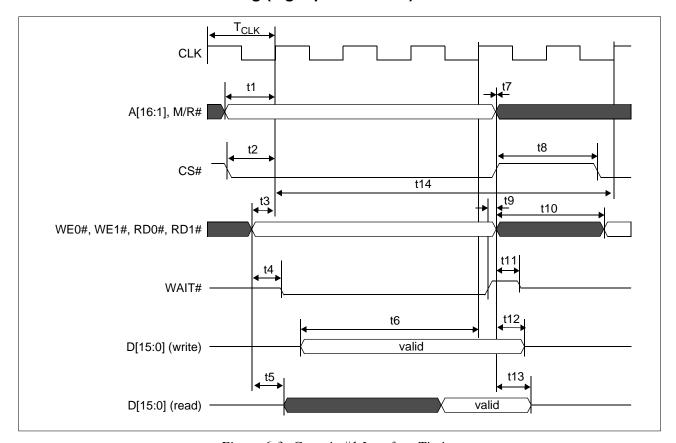

|   | 6.3.1 Generic #1 Interface Timing (e.g. Epson EOC33) |

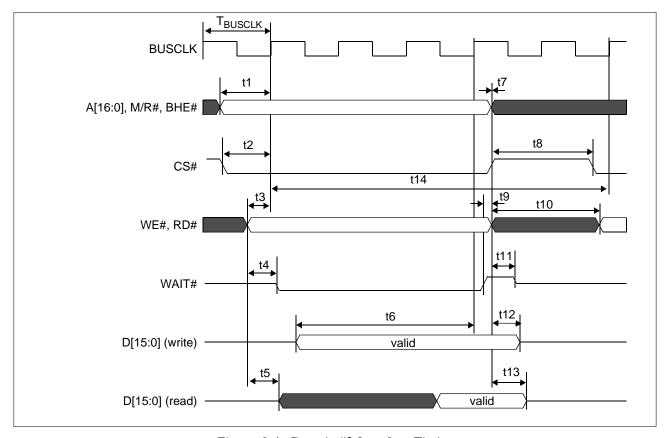

|     | 6.3.2   | Generic #2 Interface Timing (e.g. ISA)                                                  |

|-----|---------|-----------------------------------------------------------------------------------------|

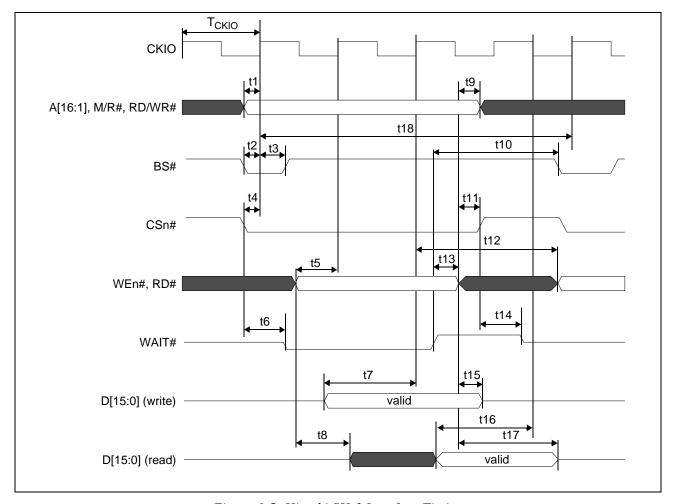

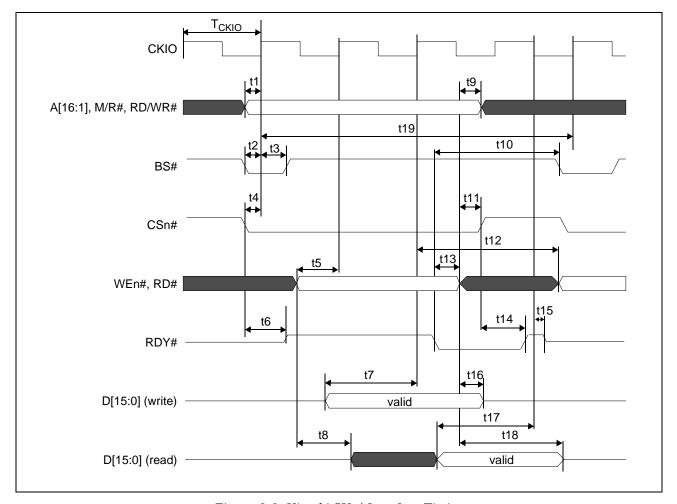

|     | 6.3.3   | Hitachi SH-3 Interface Timing                                                           |

|     | 6.3.4   | Hitachi SH-4 Interface Timing                                                           |

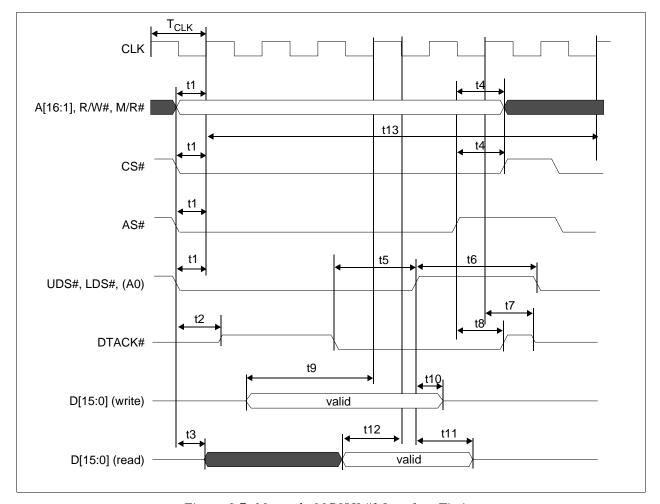

|     | 6.3.5   | Motorola MC68K #1 Interface Timing (e.g. MC68000)                                       |

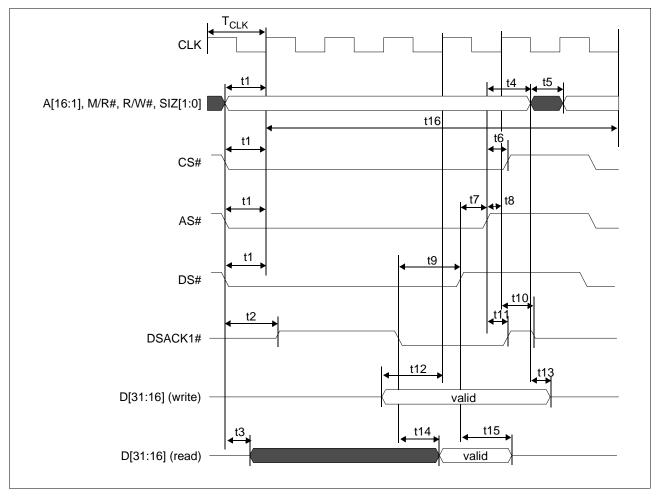

|     | 6.3.6   | Motorola MC68K #2 Interface Timing (e.g. MC68030)                                       |

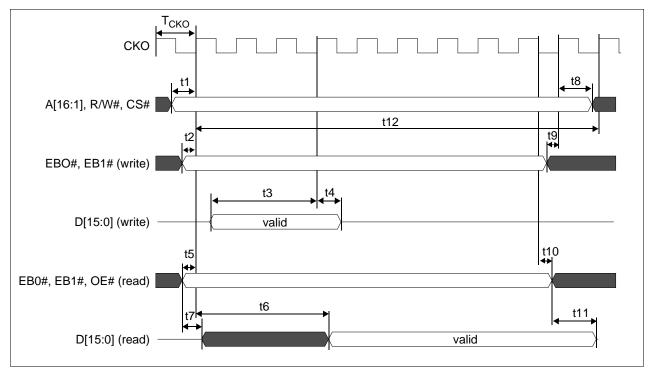

|     | 6.3.7   | Motorola REDCAP2 Interface Timing                                                       |

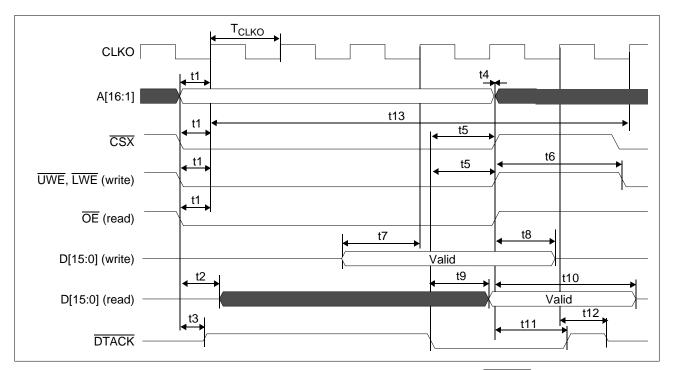

|     | 6.3.8   | $Motorola\ Dragonball\ Interface\ Timing\ with\ DTACK\ (e.g.\ MC68EZ328/MC68VZ328)\ 48$ |

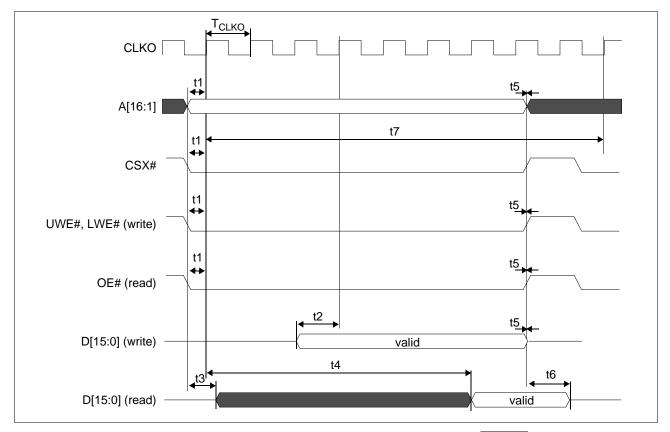

|     | 6.3.9   | $Motorola\ Dragonball\ Interface\ Timing\ w/o\ DTACK\ (e.g.\ MC68EZ328/MC68VZ328)\ 50$  |

| 6.4 | LCD     | Power Sequencing                                                                        |

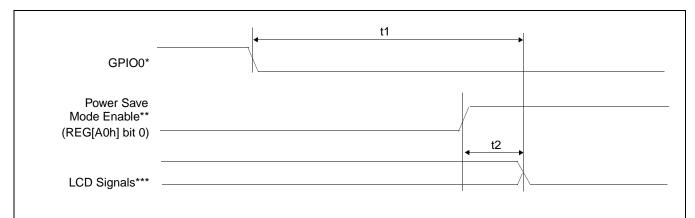

|     | 6.4.1   | Passive/TFT Power-On Sequence                                                           |

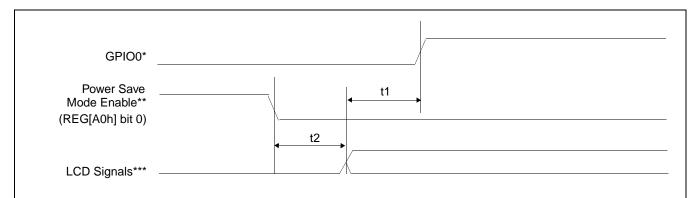

|     | 6.4.2   | Passive/TFT Power-Off Sequence                                                          |

|     | 6.4.3   | 'Direct' HR-TFT Interface Power-On/Off Sequence                                         |

| 6.5 | Displ   | ay Interface                                                                            |

|     | 6.5.1   | Generic STN Panel Timing                                                                |

|     | 6.5.2   | Single Monochrome 4-Bit Panel Timing                                                    |

|     | 6.5.3   | Single Monochrome 8-Bit Panel Timing                                                    |

|     | 6.5.4   | Single Color 4-Bit Panel Timing                                                         |

|     | 6.5.5   | Single Color 8-Bit Panel Timing (Format 1)                                              |

|     | 6.5.6   | Single Color 8-Bit Panel Timing (Format 2)                                              |

|     | 6.5.7   | Single Color 16-Bit Panel Timing                                                        |

|     | 6.5.8   | Generic TFT Panel Timing                                                                |

|     | 6.5.9   | 9/12/18-Bit TFT Panel Timing                                                            |

|     | 6.5.10  | 160x160 Sharp 'Direct' HR-TFT Panel Timing (e.g. LQ031B1DDxx) 74                        |

|     | 6.5.11  | 320x240 Sharp 'Direct' HR-TFT Panel Timing (e.g. LQ039Q2DS01) 78                        |

| 6.6 | USB     | Timing                                                                                  |

| Clo | cks .   |                                                                                         |

| 7.1 | Clock   | Descriptions                                                                            |

|     | 7.1.1   | BCLK                                                                                    |

|     | 7.1.2   | MCLK                                                                                    |

|     | 7.1.3   | PCLK                                                                                    |

|     | 7.1.4   | PWMCLK                                                                                  |

|     | 7.1.5   | USBCLK                                                                                  |

| 7.2 | Clock   | Selection                                                                               |

| 7.3 | Clock   | as versus Functions                                                                     |

| Re  | aisters |                                                                                         |

| 8.1 | _       | ter Mapping                                                                             |

| 8.2 | •       | ster Set                                                                                |

| 8.3 | U       | Register Descriptions (Offset = 0h)                                                     |

|     |         | Read-Only Configuration Registers                                                       |

7

8

|    | 8.3.2 Clock Configuration Registers                     |

|----|---------------------------------------------------------|

|    | 8.3.3 Panel Configuration Registers                     |

|    | 8.3.4 Look-Up Table Registers                           |

|    | 8.3.5 Display Mode Registers                            |

|    | 8.3.6 Picture-in-Picture Plus (PIP+) Registers          |

|    | 8.3.7 Miscellaneous Registers                           |

|    | 8.4 USB Registers (Offset = 4000h)                      |

|    | 8.5 2D Acceleration (BitBLT) Registers (Offset = 8000h) |

|    | 8.6 2D Accelerator (BitBLT) Data Register Descriptions  |

| 9  | 2D Accelerator (BitBLT) Engine                          |

|    | 9.1 Overview                                            |

|    | 9.2 BitBLT Operations                                   |

| 10 | Frame Rate Calculation                                  |

| 11 | Display Data Formats                                    |

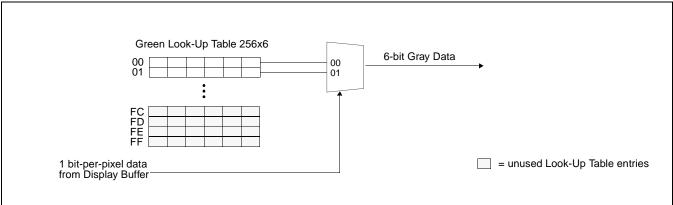

| 12 | Look-Up Table Architecture                              |

|    | 12.1 Monochrome Modes                                   |

|    | 12.2 Color Modes                                        |

| 13 | SwivelView <sup>™</sup>                                 |

|    | 13.1 Concept                                            |

|    | 13.2 90° SwivelView <sup>TM</sup>                       |

|    | 13.2.1 Register Programming                             |

|    | 13.3 180° SwivelView <sup>TM</sup>                      |

|    | 13.3.1 Register Programming                             |

|    | 13.4 270° SwivelView <sup>TM</sup>                      |

|    | 13.4.1 Register Programming                             |

| 14 | Picture-in-Picture Plus (PIP+)                          |

|    | 14.1 Concept                                            |

|    | 14.2 With SwivelView Enabled                            |

|    | 14.2.1 SwivelView 90°                                   |

|    | 14.2.2 SwivelView 180°                                  |

|    | 14.2.3 SwivelView 270°                                  |

| 15 | Power Save Mode                                         |

| 16 | Mechanical Data                                         |

| 17 | References                                              |

| 18 | Sales and Technical Support                             |

## 1 Introduction

## 1.1 Scope

This is the Hardware Functional Specification for the S1D13A04 LCD/USB Companion Chip. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at www.erd.epson.com

We appreciate your comments on our documentation. Please contact us via email at documentation@erd.epson.com.

## 1.2 Overview Description

The S1D13A04 is an LCD/USB solution designed for seamless connection to a wide variety of microprocessors. The S1D13A04 integrates a USB slave controller and an LCD graphics controller with an embedded 160K byte SRAM display buffer. The LCD controller, based on the popular S1D13706, supports all standard panel types including the Sharp HR-TFT family of products. In addition to the S1D13706 feature set, the S1D13A04 includes a Hardware Acceleration Engine to greatly improve screen drawing functions. The USB controller provides revision 1.1 compliance for applications requiring a USB client. This high level of integration provides a low cost, low power, single chip solution to meet the demands of embedded markets requiring USB client support, such as Mobile Communications devices and Palm-size PCs.

The S1D13A04 utilizes a guaranteed low-latency CPU architecture that provides support for microprocessors without READY/WAIT# handshaking signals. The 32-bit internal data path, write buffer and the Hardware Acceleration Engine provide high performance bandwidth into display memory allowing for fast display updates. 'Direct' support for the Sharp HR-TFT removes the requirement of an external Timing Control IC.

Additionally, products requiring a rotated display can take advantage of the SwivelView<sup>™</sup> feature which provides hardware rotation of the display memory transparent to the software application. The S1D13A04 also provides support for "Picture-in-Picture Plus" (a variable size Overlay window).

The S1D13A04, with its integrated USB client, provides impressive support for Palm OS<sup>®</sup> handhelds. However, its impartiality to CPU type or operating system makes it an ideal display solution for a wide variety of applications.

# 2 Features

## 2.1 Integrated Frame Buffer

• Embedded 160k byte SRAM display buffer.

#### 2.2 CPU Interface

• Direct support of the following interfaces:

Generic MPU bus interface with programmable ready (WAIT#).

Hitachi SH-4 / SH-3.

Motorola M68K.

Motorola MC68EZ328/MC68VZ328 DragonBall.

Motorola "REDCAP2" - no WAIT# signal.

- "Fixed" low-latency CPU access times.

- Registers are memory-mapped M/R# input selects between memory and register address space.

- The complete 160k byte display buffer is directly and contiguously available through the 18-bit address bus.

## 2.3 Display Support

- Single-panel, single drive passive displays.

- 4/8-bit monochrome LCD interface.

- 4/8/16-bit color LCD interface.

- Active Matrix TFT interface.

- 9/12/18-bit interface.

- 'Direct' support for 18-bit Sharp HR-TFT LCD or compatible interface.

#### 2.4 Display Modes

- 1/2/4/8/16 bit-per-pixel (bpp) color depths.

- Up to 64 gray shades on monochrome passive LCD panels.

- Up to 64K colors on passive panels.

- Up to 64K colors on active matrix LCD panels.

- Example resolutions:

320x240 at a color depth of 16 bpp 320x320 at a color depth of 8 bpp 160x160 at a color depth of 16 bpp (2 pages) 160x240 at a color depth of 16 bpp

#### 2.5 Display Features

- SwivelView<sup>TM</sup>: 90°, 180°, 270° counter-clockwise hardware rotation of display image.

- Virtual display support: displays images larger than the panel size through the use of panning and scrolling.

- Picture-in-Picture Plus (PIP<sup>+</sup>): displays a variable size window overlaid over background image.

- Pixel Doubling: independent control of both horizontal and vertical pixel doubling.

- example usage: 160x160 8 bpp can be expanded to 320x320 8 bpp without any additional memory.

- Double Buffering/Multi-pages: provides smooth animation and instantaneous screen updates.

#### 2.6 Clock Source

- Three independent clock inputs: CLKI, CLKI2 and USBCLK.

- Flexible clock source selection:

- internal Bus Clock (BCLK) selected from CLKI or CLKI/2 (CNF6)

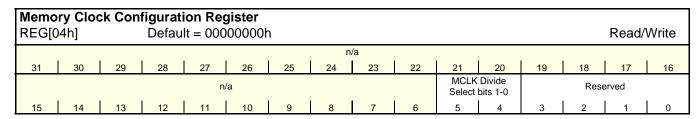

- internal Memory Clock (MCLK) selected from BCLK or BCLK divide ratio (REG[04h)

- internal Pixel Clock (PCLK) selected from CLKI, CLKI2, MCLK, or BCLK. PCLK can also be divided down from source (REG[08h])

- Single clock input possible if USB support not required.

#### 2.7 USB Device

- USB Client, revision 1.1 compliant.

- Dedicated clock input: USBCLK.

#### 2.8 2D Acceleration

• 2D BitBLT engine including:

Write BitBLT

Move BitBLT

Transparent Write BitBLT

Transparent Move BitBLT

Solid Fill BitBLT

Pattern Fill BitBLT

Color Expansion BitBLT

Move BitBLT with Color Expansion

#### 2.9 Miscellaneous

- Software Video Invert.

- Software initiated Power Save mode.

- General Purpose Input/Output pins are available.

- IO Operates at 3.3 volts  $\pm$  10%.

- Core operates at 2.0 volts  $\pm$  10% or 2.5 volts  $\pm$  10%.

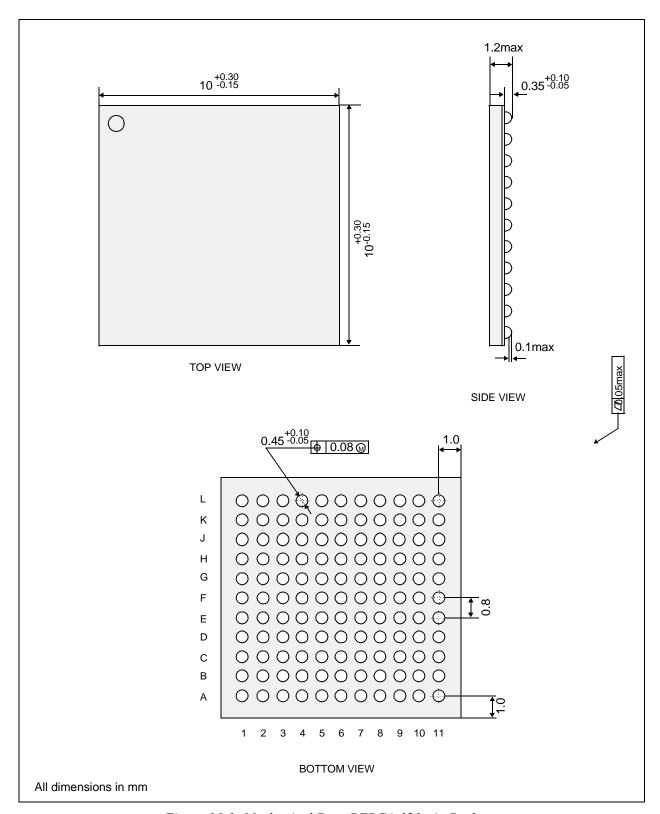

- 121-pin PFBGA package.

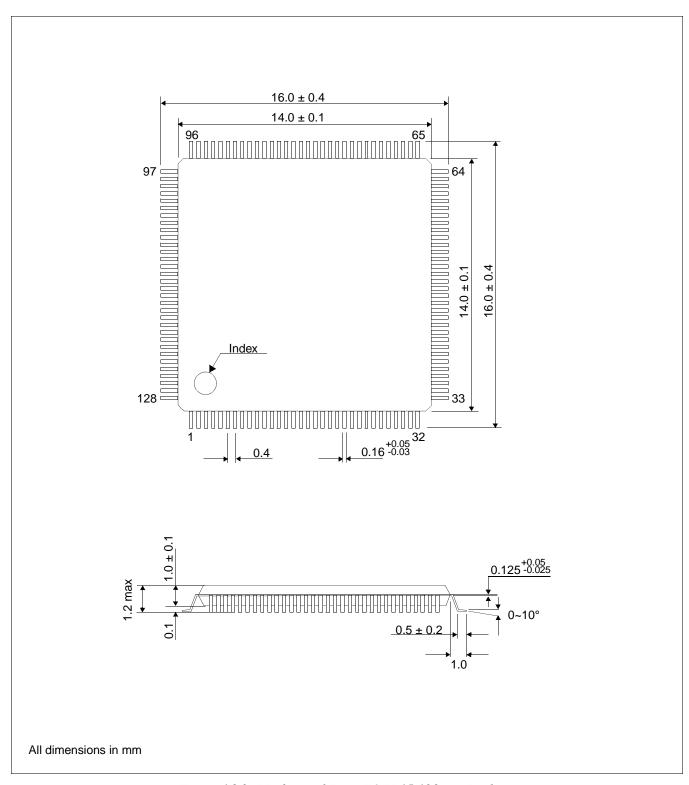

- 128-pin TQFP15 package.

# 3 Typical System Implementation Diagrams

# 3.1 Typical System Diagrams.

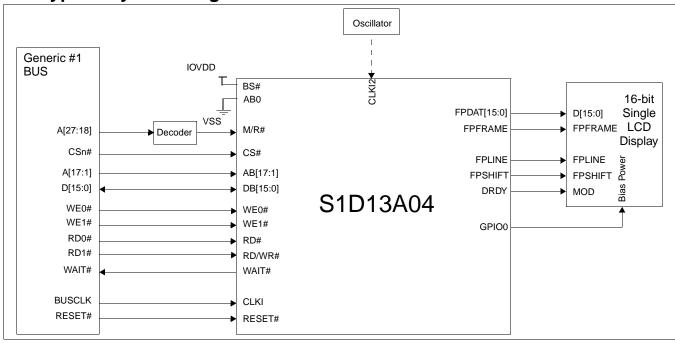

Figure 3-1: Typical System Diagram (Generic #1 Bus)

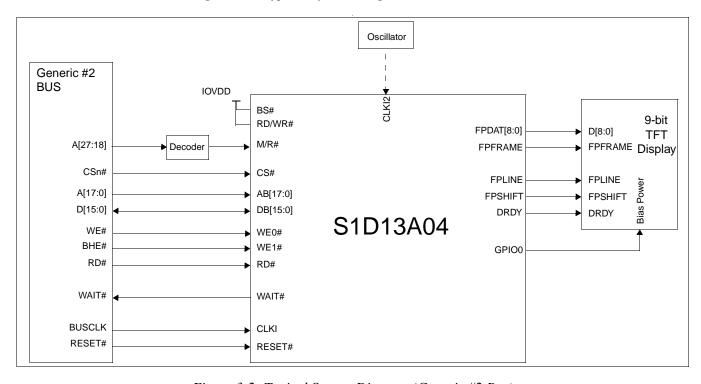

Figure 3-2: Typical System Diagram (Generic #2 Bus)

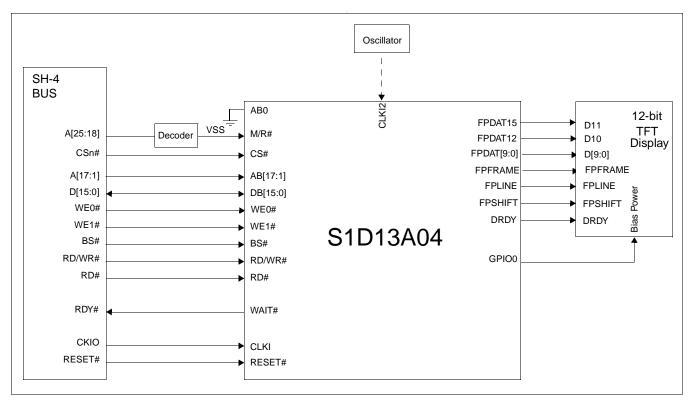

Figure 3-3: Typical System Diagram (Hitachi SH-4 Bus)

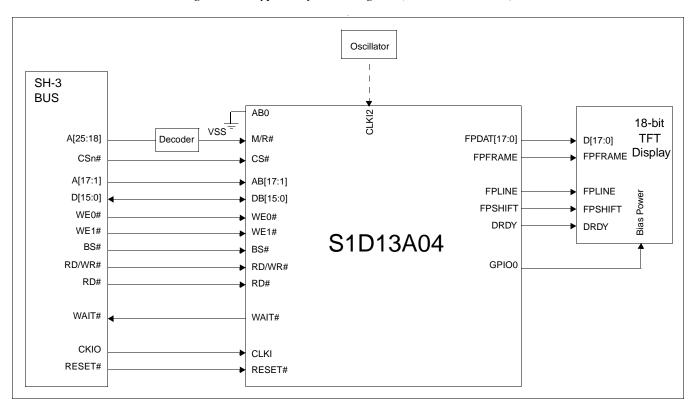

Figure 3-4: Typical System Diagram (Hitachi SH-3 Bus)

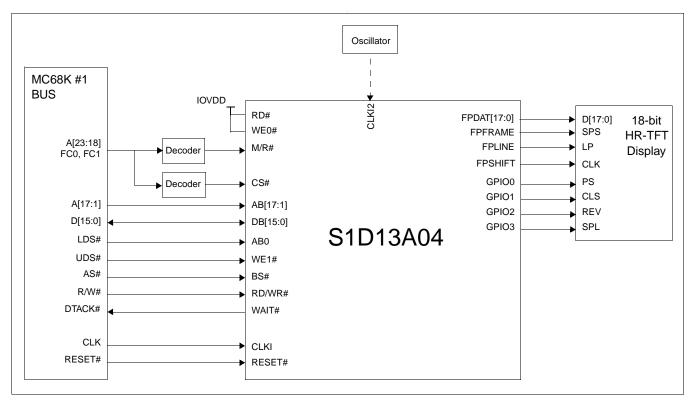

Figure 3-5: Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000)

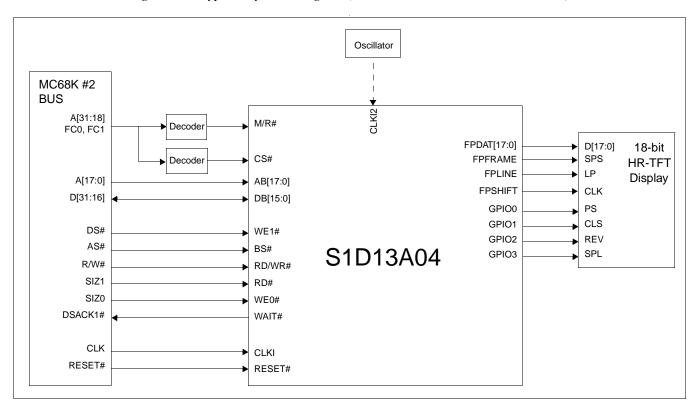

Figure 3-6: Typical System Diagram (MC68K #2, Motorola 32-Bit 68030)

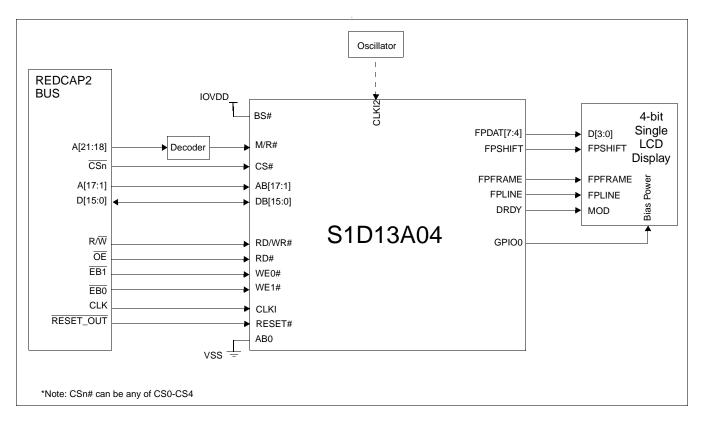

Figure 3-7: Typical System Diagram (Motorola REDCAP2 Bus)

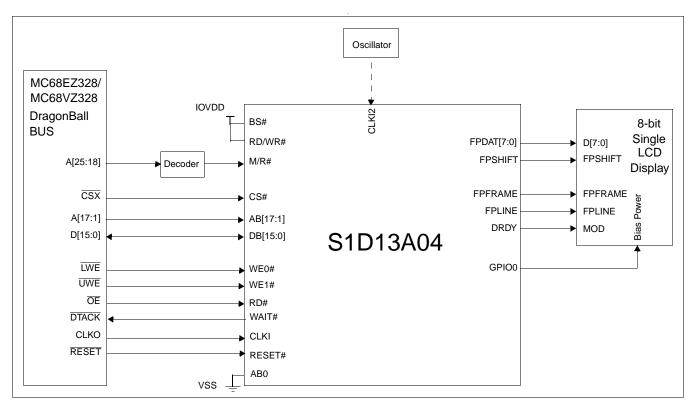

Figure 3-8: Typical System Diagram (Motorola MC68EZ328/MC68VZ328 "DragonBall" Bus)

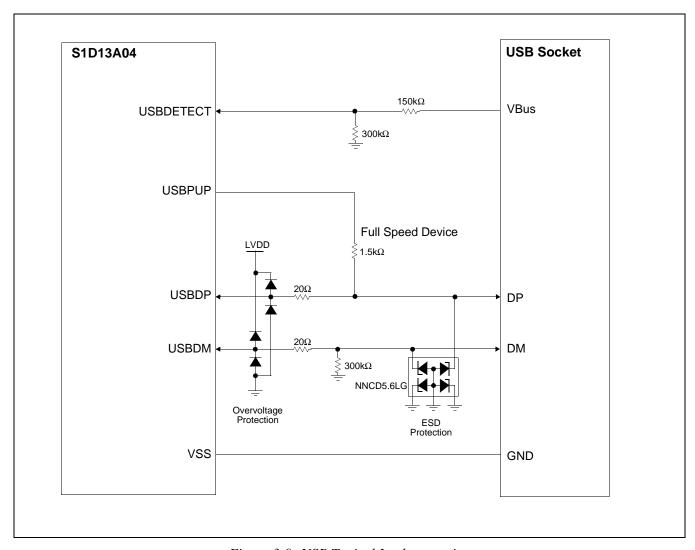

#### 3.2 USB Interface

Figure 3-9: USB Typical Implementation

### 4 Pins

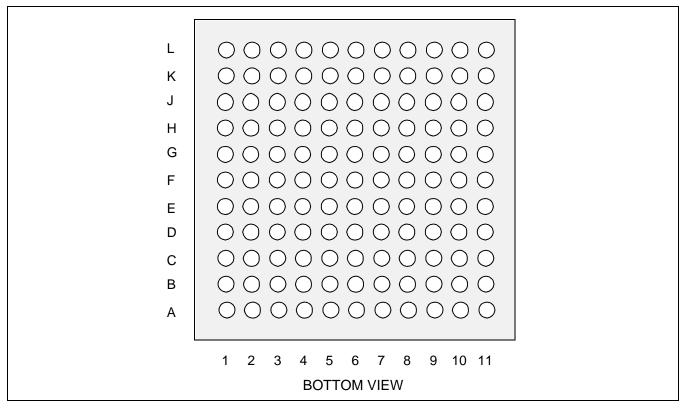

# 4.1 Pinout Diagram - PFBGA - 121-pin

Figure 4-1: Pinout Diagram - PFBGA 121-pin

| Tr 11 11          | DEDCA       | 101 .       | 11 .       |

|-------------------|-------------|-------------|------------|

| <i>Table 4-1:</i> | PFRGA       | 1 / 1 - min | Manning    |

| 10000 1 1.        | 1 1 2 0 1 1 | I I Pui     | TITOTPPING |

|   | 1      | 2       | 3      | 4     | 5    | 6     | 7      | 8       | 9       | 10      | 11      |

|---|--------|---------|--------|-------|------|-------|--------|---------|---------|---------|---------|

| Α | NC     | COREVDD | AB4    | AB7   | AB11 | AB15  | CNF0   | NC      | PWMOUT  | IOVDD   | NC      |

| В | NC     | VSS     | AB5    | NC    | AB10 | AB14  | CNF1   | CNF4    | CLKI2   | VSS     | NC      |

| С | NC     | COREVDD | AB3    | AB6   | AB9  | AB16  | CNF2   | CNF5    | CNF6    | FPDAT17 | NC      |

| D | AB0    | AB1     | AB2    | AB8   | AB12 | AB17  | CNF3   | FPDAT13 | FPDAT16 | FPDAT15 | FPDAT14 |

| E | RD#    | BS#     | M/R#   | CS#   | WE0# | AB13  | TESTEN | FPDAT9  | FPDAT12 | FPDAT11 | FPDAT10 |

| F | RESET# | VSS     | RD/WR# | WE1#  | CLKI | NC    | FPDAT8 | FPDAT6  | VSS     | FPDAT7  | IOVDD   |

| G | WAIT#  | DB15    | DB14   | IOVDD | VSS  | GPIO5 | FPDAT5 | FPDAT1  | FPDAT2  | FPDAT3  | FPDAT4  |

| Н | DB12   | DB11    | DB10   | DB13  | NC   | IOVDD | GPIO4  | NC      | FPLINE  | FPSHIFT | FPDAT0  |

| J | NC     | DB9     | DB6    | DB5   | DB2  | NC    | GPIO1  | USBCLK  | FPFRAME | COREVDD | NC      |

| K | NC     | VSS     | DB8    | DB4   | DB1  | GPIO6 | GPIO2  | IRQ     | DRDY    | VSS     | NC      |

| L | NC     | IOVDD   | DB7    | DB3   | DB0  | GPIO7 | GPIO3  | GPIO0   | IOVDD   | COREVDD | NC      |

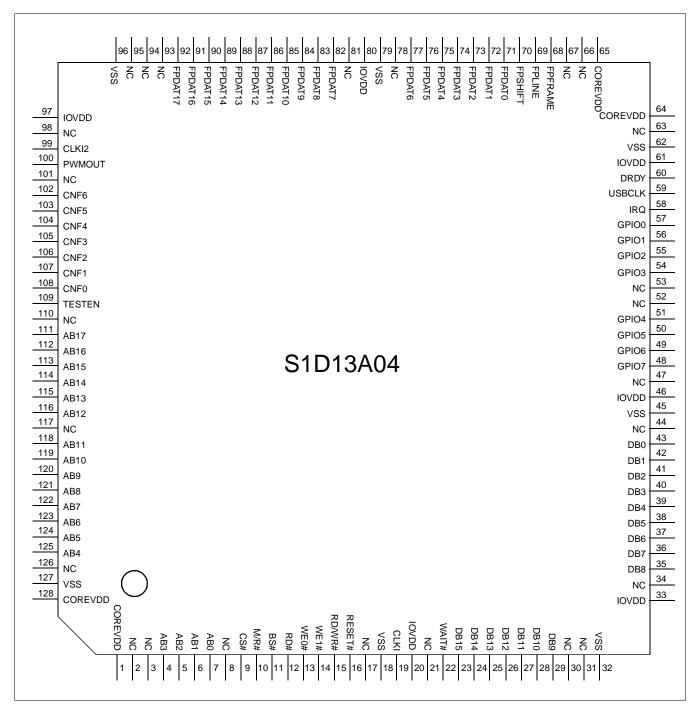

## 4.2 Pinout Diagram - TQFP15 - 128-pin

Figure 4-2: Pinout Diagram - TQFP15 128-pin

#### 4.3 Pin Descriptions

#### Key:

I = Input O = Output

IO = Bi-Directional (Input/Output)

P = Power pin CI = CMOS input LI = LVTTL input

LB2A = LVTTL IO buffer (6mA/-6mA@3.3V)

LB3P = Low noise LVTTL IO buffer (6mA/-6mA@3.3V) LO3 = Low noise LVTTL Output buffer (3mA/-3mA@3.3V)

LB3M = Low noise LVTTL IO buffer with input mask (3mA/-3mA@3.3V)

T1 = Test mode control input with pull-down resistor (typical value of  $50K\Omega$  at 3.3V)

Hi-Z = High Impedance CUS = Custom Cell Type

#### 4.3.1 Host Interface

Table 4-2: Host Interface Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin#                                                                              | TQFP15<br>Pin#              | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|--------------------------------------------------------------------------------------------|-----------------------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB0      | ı    | D1                                                                                         | 7                           | LI   | _               | <ul> <li>This input pin has multiple functions.</li> <li>For Generic #1, this pin is not used and should be connected to VSS.</li> <li>For Generic #2, this pin inputs system address bit 0 (A0).</li> <li>For SH-3/SH-4, this pin is not used and should be connected to VSS.</li> <li>For MC68K #1, this pin inputs the lower data strobe (LDS#).</li> <li>For MC68K #2, this pin inputs system address bit 0 (A0).</li> <li>For REDCAP2, this pin is not used and should be connected to VSS.</li> <li>For DragonBall, this pin is not used and should be connected to VSS.</li> <li>See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.</li> </ul> |

| AB[17:1] | ı    | D6, C6,<br>A6, B6,<br>E6, D5,<br>A5, B5,<br>C5, D4,<br>A4, C4,<br>B3, A3,<br>C3, D3,<br>D2 | 111-116,<br>118-125,<br>4-6 | CI   | _               | System address bus bits 17-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

<sup>&</sup>lt;sup>a</sup> LVTTL is Low Voltage TTL (see Section 5, "D.C. Characteristics" on page 29).

Table 4-2: Host Interface Pin Descriptions

|          | Type | PFBGA                             | TQFP15 | Call | RESET# | Deparinties                                                                                                                                                      |

|----------|------|-----------------------------------|--------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Type | Pin#                              | Pin#   | Cell | State  | Description                                                                                                                                                      |

|          |      |                                   |        |      |        | Input data from the system data bus.                                                                                                                             |

|          |      |                                   |        |      |        | For Generic #1, these pins are connected to D[15:0].                                                                                                             |

|          |      | G2, G3,                           |        |      |        | • For Generic #2, these pins are connected to D[15:0].                                                                                                           |

|          |      | H4, H1,                           |        |      |        | • For SH-3/SH-4, these pins are connected to D[15:0].                                                                                                            |

|          |      | H2, H3,                           | 23-29, |      |        | For MC68K #1, these pins are connected to D[15:0].  For MC68K #0, these pins are connected to D[15:0].  For MC68K #0, these pins are connected to D[15:0].       |

| DB[15:0] | Ю    | J2, K3,<br>L3, J3, J4,<br>K4, L4, | 35-43  | LB2A | Hi-Z   | <ul> <li>For MC68K #2, these pins are connected to D[31:16] for<br/>a 32-bit device (e.g. MC68030) or D[15:0] for a 16-bit<br/>device (e.g. MC68340).</li> </ul> |

|          |      | J5, K5, L5                        |        |      |        | For REDCAP2, these pins are connected to D[15:0].                                                                                                                |

|          |      | , ,                               |        |      |        | <ul> <li>For DragonBall, these pins are connected to D[15:0].</li> </ul>                                                                                         |

|          |      |                                   |        |      |        | See Table 4-8: "Host Bus Interface Pin Mapping," on page 27                                                                                                      |

|          |      |                                   |        |      |        | for summary.                                                                                                                                                     |

|          |      |                                   |        |      |        | This input pin has multiple functions.                                                                                                                           |

|          |      |                                   |        |      |        | <ul> <li>For Generic #1, this pin inputs the write enable signal for<br/>the lower data byte (WE0#).</li> </ul>                                                  |

|          |      |                                   | 13     | LI   |        | For Generic #2, this pin inputs the write enable signal (WE#)                                                                                                    |

|          |      | <b>E</b> 5                        |        |      |        | <ul> <li>For SH-3/SH-4, this pin inputs the write enable signal for<br/>data byte 0 (WE0#).</li> </ul>                                                           |

| WE0#     | I    |                                   |        |      |        | <ul> <li>For MC68K #1, this pin must be tied to IO V<sub>DD</sub></li> </ul>                                                                                     |

|          |      |                                   |        |      |        | For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).                                                                                                         |

|          |      |                                   |        |      |        | <ul> <li>For REDCAP2, this pin inputs the byte enable signal for<br/>the D[7:0] data byte (EB1).</li> </ul>                                                      |

|          |      |                                   |        |      |        | <ul> <li>For DragonBall, this pin inputs the byte enable signal for<br/>the D[7:0] data byte (LWE).</li> </ul>                                                   |

|          |      |                                   |        |      |        | See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.                                                                                         |

|          |      |                                   |        |      |        | This input pin has multiple functions.                                                                                                                           |

|          |      |                                   |        |      |        | <ul> <li>For Generic #1, this pin inputs the write enable signal for<br/>the upper data byte (WE1#).</li> </ul>                                                  |

|          |      |                                   |        |      |        | <ul> <li>For Generic #2, this pin inputs the byte enable signal for<br/>the high data byte (BHE#).</li> </ul>                                                    |

|          |      |                                   |        |      |        | <ul> <li>For SH-3/SH-4, this pin inputs the write enable signal for<br/>data byte 1 (WE1#).</li> </ul>                                                           |

| WE1#     | I    | F4                                | 14     | LI   | _      | For MC68K #1, this pin inputs the upper data strobe (UDS#).                                                                                                      |

|          |      |                                   |        |      |        | For MC68K #2, this pin inputs the data strobe (DS#).                                                                                                             |

|          |      |                                   |        |      |        | <ul> <li>For REDCAP2, this pin inputs the byte enable signal for<br/>the D[15:8] data byte (EB0).</li> </ul>                                                     |

|          |      |                                   |        |      |        | <ul> <li>For DragonBall, this pin inputs the byte enable signal for<br/>the D[15:8] data byte (UWE).</li> </ul>                                                  |

|          |      |                                   |        |      |        | See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.                                                                                         |

| CS#      | ı    | E4                                | 9      | CI   | _      | Chip select input. See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.                                                                      |

Table 4-2: Host Interface Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin# | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|---------------|----------------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M/R#     | ı    | E3            | 10             | LI   | _               | This input pin is used to select between the display buffer and register address spaces of the S1D13A04. M/R# is set high to access the display buffer and low to access the registers. See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BS#      | 1    | E2            | 11             | LI   | _               | This input pin has multiple functions.  For Generic #1, this pin must be tied to IO V <sub>DD</sub> .  For Generic #2, this pin must be tied to IO V <sub>DD</sub> .  For SH-3/SH-4, this pin inputs the bus start signal (BS#).  For MC68K #1, this pin inputs the address strobe (AS#).  For MC68K #2, this pin inputs the address strobe (AS#).  For REDCAP2, this pin must be tied to IO V <sub>DD</sub> .  For DragonBall, this pin must be tied to IO V <sub>DD</sub> .  See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.                                                                                                                             |

| RD/WR#   | 1    | F3            | 15             | LI   | _               | <ul> <li>This input pin has multiple functions.</li> <li>For Generic #1, this pin inputs the read command for the upper data byte (RD1#).</li> <li>For Generic #2, this pin must be tied to IO V<sub>DD</sub>.</li> <li>For SH-3/SH-4, this pin inputs the RD/WR# signal. The S1D13A04 needs this signal for early decode of the bus cycle.</li> <li>For MC68K #1, this pin inputs the R/W# signal.</li> <li>For MC68K #2, this pin inputs the R/W# signal.</li> <li>For REDCAP2, this pin inputs the R/W signal.</li> <li>For DragonBall, this pin must be tied to IO V<sub>DD</sub>.</li> <li>See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.</li> </ul> |

| RD#      | ı    | E1            | 12             | LI   | _               | <ul> <li>This input pin has multiple functions.</li> <li>For Generic #1, this pin inputs the read command for the lower data byte (RD0#).</li> <li>For Generic #2, this pin inputs the read command (RD#).</li> <li>For SH-3/SH-4, this pin inputs the read signal (RD#).</li> <li>For MC68K #1, this pin must be tied to IO V<sub>DD</sub>.</li> <li>For MC68K #2, this pin inputs the bus size bit 1 (SIZ1).</li> <li>For REDCAP2, this pin inputs the output enable (OE).</li> <li>For DragonBall, this pin inputs the output enable (OE).</li> <li>See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.</li> </ul>                                          |

Table 4-2: Host Interface Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin # | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|----------------|----------------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT#    | IO   | Pin #          | Pin#           | LB2A | State Hi-Z      | During a data transfer, this output pin is driven active to force the system to insert wait states. It is driven inactive to indicate the completion of a data transfer. WAIT# is released to the high impedance state after the data transfer is complete. Its active polarity is configurable. See Table 4-7: "Summary of Power-On/Reset Options," on page 26.  • For Generic #1, this pin outputs the wait signal (WAIT#).  • For Generic #2, this pin outputs the wait request signal (WAIT#).  • For SH-3 mode, this pin outputs the wait request signal (WAIT#).  • For SH-4 mode, this pin outputs the device ready signal (RDY#).  • For MC68K #1, this pin outputs the data transfer acknowledge signal (DTACK#).  • For MC68K #2, this pin outputs the data transfer and size acknowledge bit 1 (DSACK1#).  • For PagonBall, this pin outputs the data transfer acknowledge signal (DTACK).  See Table 4-8: "Host Bus Interface Pin Mapping," on page 27 for summary.  Note: This pin should be tied to the inactive voltage level as selected by CNF5, using a pull-up or pull-down resistor. If |

|          |      |                |                |      |                 | CNF5 = 1, the WAIT# pin should be tied low using a pull-down resistor. If CNF5 = 0, the WAIT# pin should be tied low using a pull-down resistor. If CNF5 = 0, the WAIT# pin should be tied high using a pull-up resistor. If WAIT# is not used, this pin should be tied either high or low using a pull-up or pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RESET#   | I    | F1             | 16             | LI   | _               | Active low input to set all internal registers to the default state and to force all signals to their inactive states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### 4.3.2 LCD Interface

Table 4-3: LCD Interface Pin Descriptions

| Pin Name    | Туре | PFBGA<br>Pin#                                                                                           | TQFP15<br>Pin#                                                                                 | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPDAT[17:0] | 0    | C10, D9,<br>D10, D11,<br>D8, E9,<br>E10, E11,<br>E8, F7,<br>F10, F8,<br>G7, G11,<br>G10, G9,<br>G8, H11 | 92, 91,<br>90, 89,<br>88, 87,<br>86, 85,<br>84, 83,<br>82, 77,<br>76, 75,<br>74, 73,<br>72, 71 | LB3P | 0               | Panel Data bits 17-0.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FPFRAME     | 0    | J9                                                                                                      | 68                                                                                             | LB3P | 0               | This output pin has multiple functions.  • Frame Pulse  • SPS for 'Direct' HR-TFT  See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                                                                                                               |

| FPLINE      | 0    | Н9                                                                                                      | 69                                                                                             | LB3P | 0               | This output pin has multiple functions.  • Line Pulse  • LP for 'Direct' HR-TFT  See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                                                                                                                 |

| FPSHIFT     | 0    | H10                                                                                                     | 70                                                                                             | LB3P | 0               | This output pin has multiple functions.  • Shift Clock  • CLK for 'Direct' HR-TFT  See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                                                                                                               |

| DRDY        | 0    | K9                                                                                                      | 60                                                                                             | LO3  | 0               | This output pin has multiple functions.  • Display enable (DRDY) for TFT panels  • 2nd shift clock (FPSHIFT2) for passive LCD with Format 1 interface  • LCD backplane bias signal (MOD) for all other LCD panels  • General Purpose Output  See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                     |

| GPIO0       | Ю    | L8                                                                                                      | 57                                                                                             | LB3M | _               | This pin has multiple functions.  • PS for 'Direct' HR-TFT  • General purpose IO pin 0 (GPIO0)  GPIO0 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is used for HR-TFT, it must be configured as an output using REG[64h]. Otherwise, it must either be configured as an output or be pulled high or low externally to avoid unnecessary current drain.  See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary. |

Table 4-3: LCD Interface Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin# | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                 |

|----------|------|---------------|----------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |               |                |      |                 | This pin has multiple functions.  • CLS for 'Direct' HR-TFT  • General purpose IO pin 1 (GPIO1)                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                 |

| GPIO1    | Ю    | J7            | 56             | LB3M | _               | GPIO1 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is used for HR-TFT, it must be configured as an output using REG[64h]. Otherwise, it must either be configured as an output or be pulled high or low externally to avoid unnecessary current drain. |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | This pin has multiple functions.                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | REV for 'Direct' HR-TFT                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |

|          |      | К7            | 55             |      |                 | General purpose IO pin 2 (GPIO2)                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

| GPIO2    | Ю    |               |                | LB3M | _               | GPIO2 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is used for HR-TFT, it must be configured as an output using REG[64h]. Otherwise, it must either be configured as an output or be pulled high or low externally to avoid unnecessary current drain. |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | This pin has multiple functions.                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | SPL for 'Direct' HR-TFT                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | General purpose IO pin 3 (GPIO3)                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

| GPIO3    | Ю    | Ю             | L7             | 54   | LB3M            | _                                                                                                                                                                                                                                                                                                               | GPIO3 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is used for HR-TFT, it must be configured as an output using REG[64h]. Otherwise, it must either be configured as an output or be pulled high or low externally to avoid unnecessary current drain. |

|          |      |               |                |      |                 | See Table 4.6 "LCD Interface Pin Mapping," on page 28 for summary.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | This pin has multiple functions.                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | • USBPUP                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                 |

|          |      |               |                |      |                 | General purpose IO pin 4 (GPIO4)                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                 |

| GPIO4    | Ю    | H7            | 51             | LB3M | _               | GPIO4 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is not used for USB, it must either be configured as an output using REG[64h] or be pulled high or low externally to avoid unnecessary current drain.                                               |                                                                                                                                                                                                                                                                                                                 |

Table 4-3: LCD Interface Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin# | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------|------|---------------|----------------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO5    | Ю    | G6            | 50             | LB3M | _               | This pin has multiple functions.  • USBDETECT  • General purpose IO pin 5 (GPIO5)  GPIO5 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is not used for USB, it must either be configured as an output using REG[64h] or be pulled high or low externally to avoid                                                |

| GPIO6    | Ю    | K6            | 49             | CUS  | _               | unnecessary current drain.  This pin has multiple functions.  USBDM  General purpose IO pin 6 (GPIO6)  GPIO6 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is not used for USB, it must either be configured as an output using REG[64h] or be pulled high or low externally to avoid unnecessary current drain. |

| GPIO7    | Ю    | L6            | 48             | CUS  | _               | This pin has multiple functions.  • USBDP  • General purpose IO pin 7  GPIO7 defaults to a Hi-Z state during every RESET and defaults to an input after every RESET. When this pin is not used for USB, it must either be configured as an output using REG[64h] or be pulled high or low externally to avoid unnecessary current drain.                                 |

| IRQ      | 0    | K8            | 58             | LO3  | 0               | This output pin is the IRQ pin for USB. When IRQ is activated, an active high pulse is generated and stays high until the IRQ is serviced by software at REG[404Ah] or REG[404Ch].                                                                                                                                                                                       |

| PWMOUT   | 0    | А9            | 100            | LO3  | 0               | This pin has multiple functions.  PWM Clock output  General purpose output                                                                                                                                                                                                                                                                                               |

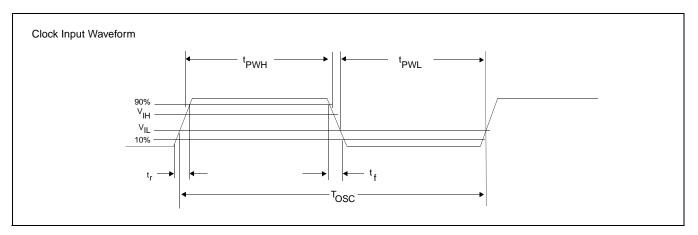

#### 4.3.3 Clock Input

Table 4-4: Clock Input Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin# | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                         |

|----------|------|---------------|----------------|------|-----------------|---------------------------------------------------------------------|

| CLKI     | I    | F5            | 19             | CI   | _               | Typically used as input clock source for bus clock and memory clock |

| CLKI2    | I    | В9            | 99             | CI   | _               | Typically used as input clock source for pixel clock                |

| USBCLK   | I    | J8            | 59             | LI   | _               | Typically used as input clock source for USB                        |

#### 4.3.4 Miscellaneous

Table 4-5: Miscellaneous Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin#      | TQFP15<br>Pin# | Cell | RESET#<br>State | Description                                                                                                                                         |

|----------|------|--------------------|----------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | C9, C8,<br>B8, D7, |                |      |                 | These inputs are used to configure the S1D13A04 - see Table 4-7: "Summary of Power-On/Reset Options," on page 26.                                   |

| CNF[6:0] | I    | C7, B7,<br>A7      | 102-108        | CI   | _               | Note: These pins are used for configuration of the S1D13A04 and must be connected directly to IO $V_{DD}$ or $V_{SS}$ .                             |

| TESTEN   | I    | E7                 | 109            | T1   | _               | Test Enable input used for production test only (has type 1 pull-down resistor with a typical value of $50 \mathrm{K}\Omega$ at $3.3 \mathrm{V}$ ). |

|          |      |                    |                |      |                 | Note: This pin must not be connected.                                                                                                               |

#### 4.3.5 Power And Ground

Table 4-6: Power And Ground Pin Descriptions

| Pin Name | Туре | PFBGA<br>Pin#                         | TQFP15<br>Pin#                       | Cell | RESET#<br>State | Description                                                                                                   |  |

|----------|------|---------------------------------------|--------------------------------------|------|-----------------|---------------------------------------------------------------------------------------------------------------|--|

| IOVDD    | Р    | L2, G4,<br>H6, L9,<br>A10, F11        | 20, 33,<br>46, 61,<br>80, 97         | Р    | _               | 6 IO V <sub>DD</sub> pins.                                                                                    |  |

| COREVDD  | Р    | A2, C2,<br>L10, J10                   | 1, 64-65,<br>128                     | Р    | _               | 2 double-bonded Core V <sub>DD.</sub> pins on TQFP package.<br>4 Core V <sub>DD.</sub> pins on PFBGA package. |  |

| VSS      | Р    | B2, F2,<br>K2, G5,<br>F9, B10,<br>K10 | 18, 32,<br>45, 62,<br>79, 96,<br>127 | Р    | _               | 7 V <sub>SS</sub> pins.                                                                                       |  |

# 4.4 Summary of Configuration Options

These pins are used for configuration of the S1D13A04 and must be connected directly to  $IOV_{DD}$  or  $V_{SS}$ . The state of CNF[6:0] are latched on the rising edge of RESET#. Changing state at any other time has no effect.

Table 4-7: Summary of Power-On/Reset Options

| S1D13A04            |                      |             |                      | Powe | er-On/Reset State                            |

|---------------------|----------------------|-------------|----------------------|------|----------------------------------------------|

| Configuration Input | 1 (con               | nected to   | O IO V <sub>DD</sub> | )    | 0 (connected to V <sub>SS</sub> )            |

|                     | Select host bus into | erface as   | follows:             |      |                                              |

|                     | CNF4                 | CNF2        | CNF1                 | CNF0 | Host Bus                                     |

|                     | 1                    | 0           | 0                    | 0    | SH-4/SH-3 interface, Big Endian              |

|                     | 0                    | 0           | 0                    | 0    | SH-4/SH-3 interface, Little Endian           |

|                     | 1                    | 0           | 0                    | 1    | MC68K #1, Big Endian                         |

|                     | 0                    | 0           | 0                    | 1    | Reserved                                     |

|                     | 1                    | 0           | 1                    | 0    | MC68K #2, Big Endian                         |

|                     | 0                    | 0           | 1                    | 0    | Reserved                                     |

| CNF4,CNF[2:0]       | 1                    | 0           | 1                    | 1    | Generic #1, Big Endian                       |

|                     | 0                    | 0           | 1                    | 1    | Generic #1, Little Endian                    |

|                     | 1                    | 1           | 0                    | 0    | Reserved                                     |

|                     | 0                    | 1           | 0                    | 0    | Generic #2, Little Endian                    |

|                     | 1                    | 1           | 0                    | 1    | REDCAP2, Big Endian                          |

|                     | 0                    | 1           | 0                    | 1    | Reserved                                     |

|                     | 1                    | 1           | 1                    | 0    | DragonBall (MC68EZ328/MC68VZ328), Big Endian |

|                     | 0                    | 1           | 1                    | 0    | Reserved                                     |

|                     | X                    | 1           | 1                    | 1    | Reserved                                     |

| CNF3                | Reserved. Must be    | set to 1.   |                      |      |                                              |

| CNF5<br>(see note)  | WAIT# is active hig  | gh          |                      |      | WAIT# is active low                          |

| CNF6                | CLKI to BCLK divid   | de ratio 2: | 1                    |      | CLKI to BCLK divide ratio 1:1                |

#### Note

If CNF5 = 1, the WAIT# pin should be tied low using a pull-down resistor. If CNF5 = 0, the WAIT# pin should be tied high using a pull-up resistor. If WAIT# is not used, this pin should be tied either high or low using a pull-up or pull-down resistor.

# 4.5 Host Bus Interface Pin Mapping

Table 4-8: Host Bus Interface Pin Mapping

| S1D13A04<br>Pin Name | Generic #1      | Generic #2                      | Hitachi<br>SH-3 /SH-4 | Motorola<br>MC68K #1            | Motorola<br>MC68K #2 | Motorola<br>REDCAP2 | Motorola<br>MC68EZ328/<br>MC68VZ328<br>DragonBall |

|----------------------|-----------------|---------------------------------|-----------------------|---------------------------------|----------------------|---------------------|---------------------------------------------------|

| AB[17:1]             | A[17:1]         | A[17:1]                         | A[17:1]               | A[17:1]                         | A[17:1]              | A[17:1]             | A[17:1]                                           |

| AB0                  | A0 <sup>1</sup> | A0                              | A0 <sup>1</sup>       | LDS#                            | A0                   | A0 <sup>1</sup>     | A0 <sup>1</sup>                                   |

| DB[15:0]             | D[15:0]         | D[15:0]                         | D[15:0]               | D[15:0]                         | D[15:0] <sup>2</sup> | D[15:0]             | D[15:0]                                           |

| CS#                  | External        | Decode                          | CSn#                  | External                        | Decode               | CSn                 | CSX                                               |

| M/R#                 |                 |                                 |                       | External Decode                 | )                    |                     |                                                   |

| CLKI                 | BUSCLK          | BUSCLK                          | CKIO                  | CLK                             | CLK                  | CLK                 | CLKO                                              |

| BS#                  | Connected       | to IO V <sub>DD</sub>           | BS#                   | AS#                             | AS#                  | Connected           | to IO V <sub>DD</sub>                             |

| RD/WR#               | RD1#            | Connected to IO V <sub>DD</sub> | RD/WR#                | R/W#                            | R/W#                 | R/W                 | Connected to IO V <sub>DD</sub>                   |

| RD#                  | RD0#            | RD#                             | RD#                   | Connected to IO V <sub>DD</sub> | SIZ1                 | ŌĒ                  | ŌĒ                                                |

| WE0#                 | WE0#            | WE#                             | WE0#                  | Connected to IO V <sub>DD</sub> | SIZ0                 | EB1                 | LWE                                               |

| WE1#                 | WE1#            | BHE#                            | WE1#                  | UDS#                            | DS#                  | EB0                 | UWE                                               |

| WAIT#                | WAIT#           | WAIT#                           | WAIT#/<br>RDY#        | DTACK#                          | DSACK1#              | N/A                 | DTACK                                             |

| RESET#               | RESET#          | RESET#                          | RESET#                | RESET#                          | RESET#               | RESET_OUT           | RESET                                             |

<sup>&</sup>lt;sup>1</sup> A0 for these busses is not used internally by the S1D13A04 and should be connected to  $V_{SS}$ .  $^2$  If the target MC68K bus is 32-bit, then these signals should be connected to D[31:16].

## 4.6 LCD Interface Pin Mapping

Table 4-9: LCD Interface Pin Mapping

|          | Monoc<br>Passive | hrome<br>e Panel |                      | Color Pass           | ive Panel            |                       |          | Color Ti | FT Panel |                     |

|----------|------------------|------------------|----------------------|----------------------|----------------------|-----------------------|----------|----------|----------|---------------------|

| Pin Name | Cin              | ngle             |                      | Sing                 | gle                  |                       |          | Others   |          | 'Direct'            |

|          | SII              | igie             |                      | Format 1             | Format 2             |                       |          | Others   |          | HR-TFT <sup>1</sup> |

|          | 4-bit            | 8-bit            | 4-bit                | 8-bit                | 8-bit                | 16-Bit                | 9-bit    | 12-bit   | 18-bit   | 18-bit              |

| FPFRAME  | FPFRAME          |                  |                      |                      |                      |                       |          |          | SPS      |                     |

| FPLINE   | FPLINE           |                  |                      |                      |                      |                       |          | LP       |          |                     |

| FPSHIFT  |                  |                  |                      |                      | FPSHIFT              |                       |          |          |          | DCLK                |

| DRDY     |                  | MOD              |                      | FPSHIFT2             |                      | OD                    |          | DRDY     |          | GPO <sup>2</sup>    |

| FPDAT0   | driven 0         | D0               | driven 0             | D0 (B5) <sup>3</sup> | D0 (G3) <sup>3</sup> | D0 (R6) <sup>3</sup>  | R2       | R3       | R5       | R5                  |

| FPDAT1   | driven 0         | D1               | driven 0             | D1 (R5) <sup>3</sup> | D1 (R3) <sup>3</sup> | D1 (G5) <sup>3</sup>  | R1       | R2       | R4       | R4                  |

| FPDAT2   | driven 0         | D2               | driven 0             | D2 (G4) <sup>3</sup> | D2 (B2) <sup>3</sup> | D2 (B4) <sup>3</sup>  | R0       | R1       | R3       | R3                  |

| FPDAT3   | driven 0         | D3               | driven 0             | D3 (B3) <sup>3</sup> | D3 (G2) <sup>3</sup> | D3 (R4) <sup>3</sup>  | G2       | G3       | G5       | G5                  |

| FPDAT4   | D0               | D4               | D0 (R2) <sup>3</sup> | D4 (R3) <sup>3</sup> | D4 (R2) <sup>3</sup> | D8 (B5) <sup>3</sup>  | G1       | G2       | G4       | G4                  |

| FPDAT5   | D1               | D5               | D1 (B1) <sup>3</sup> | D5 (G2) <sup>3</sup> | D5 (B1) <sup>3</sup> | D9 (R5) <sup>3</sup>  | G0       | G1       | G3       | G3                  |

| FPDAT6   | D2               | D6               | D2 (G1) <sup>3</sup> | D6 (B1) <sup>3</sup> | D6 (G1) <sup>3</sup> | D10 (G4) <sup>3</sup> | B2       | B3       | B5       | B5                  |

| FPDAT7   | D3               | D7               | D3 (R1) <sup>3</sup> | D7 (R1) <sup>3</sup> | D7 (R1) <sup>3</sup> | D11 (B3) <sup>3</sup> | B1       | B2       | B4       | B4                  |

| FPDAT8   | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D4 (G3) <sup>3</sup>  | В0       | B1       | В3       | B3                  |

| FPDAT9   | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D5 (B2) <sup>3</sup>  | driven 0 | R0       | R2       | R2                  |

| FPDAT10  | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D6 (R2) <sup>3</sup>  | driven 0 | driven 0 | R1       | R1                  |

| FPDAT11  | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D7 (G1) <sup>3</sup>  | driven 0 | driven 0 | R0       | R0                  |

| FPDAT12  | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D12 (R3) <sup>3</sup> | driven 0 | G0       | G2       | G2                  |

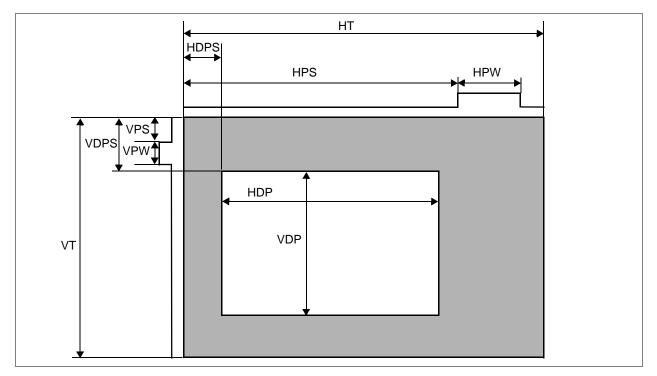

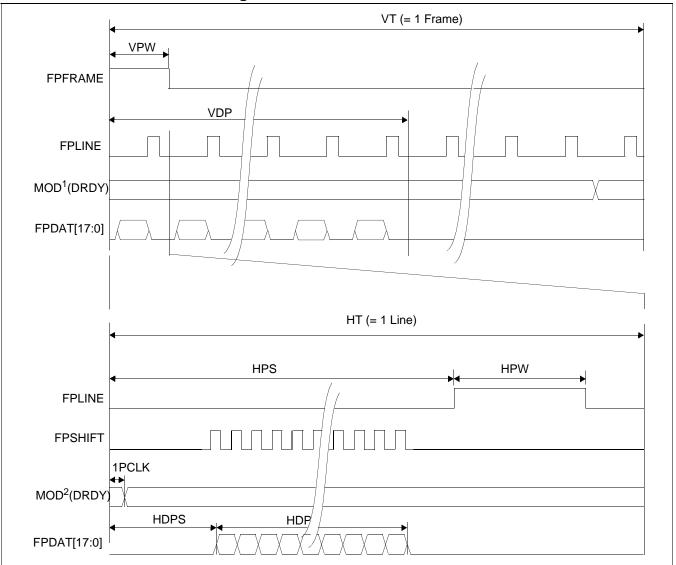

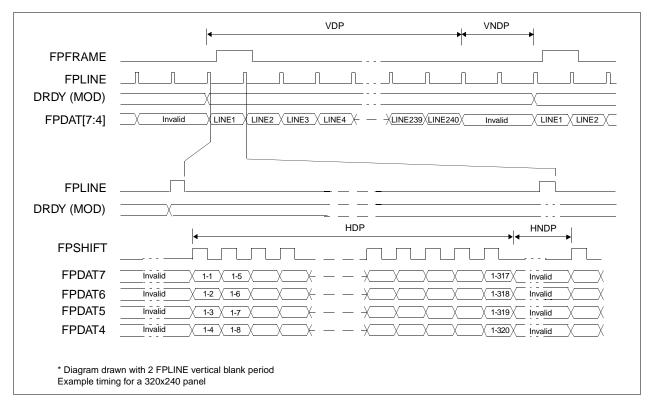

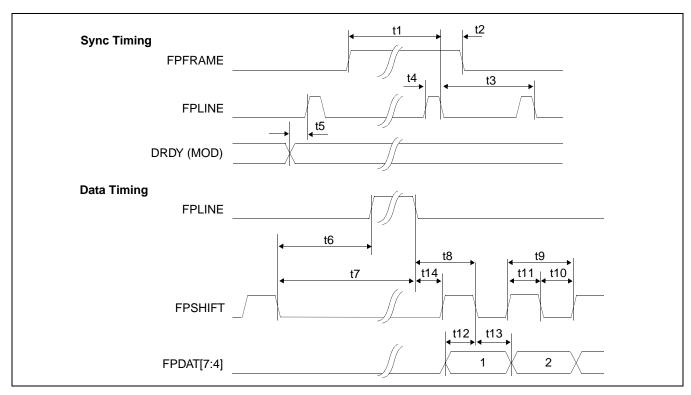

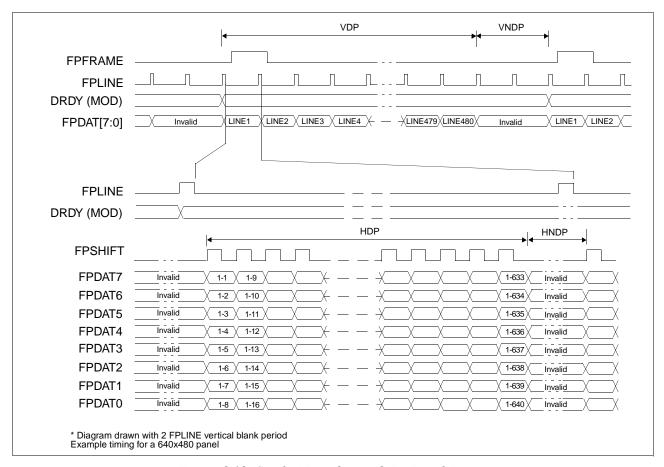

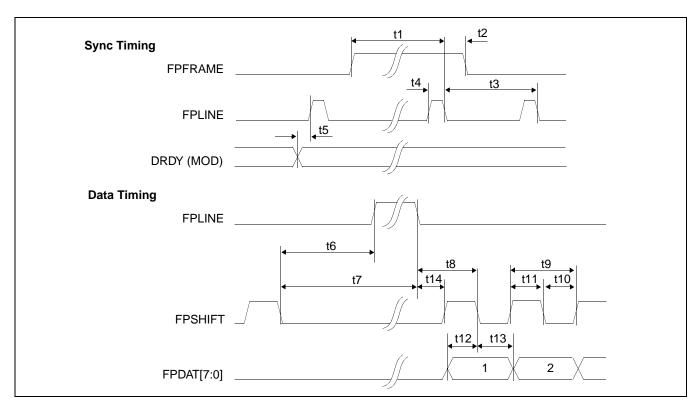

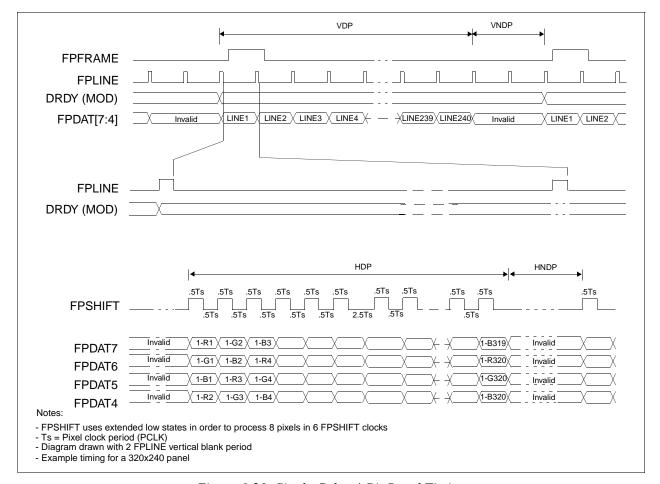

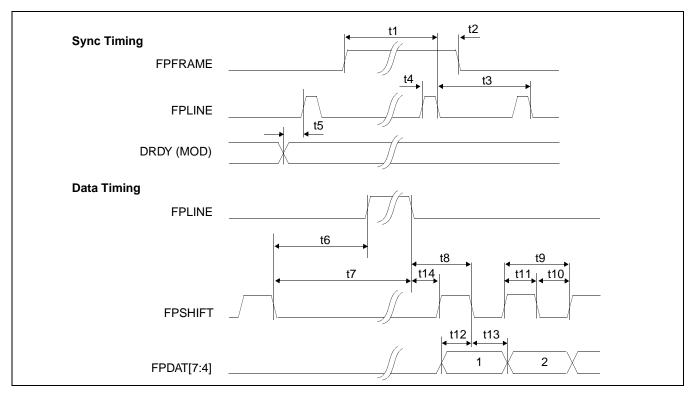

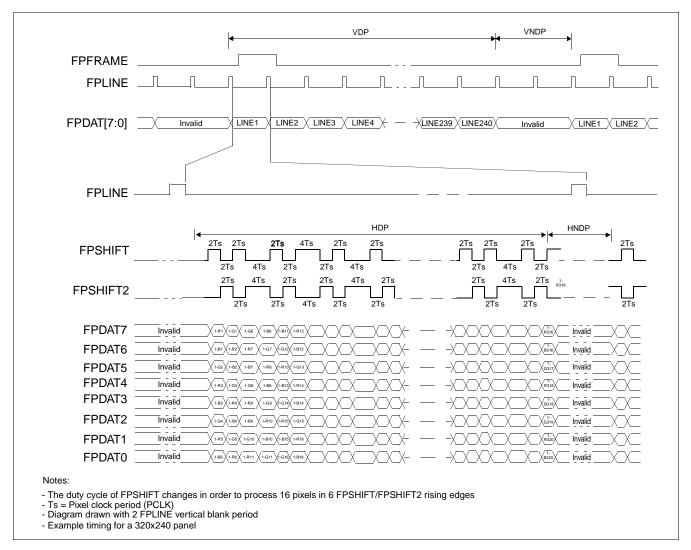

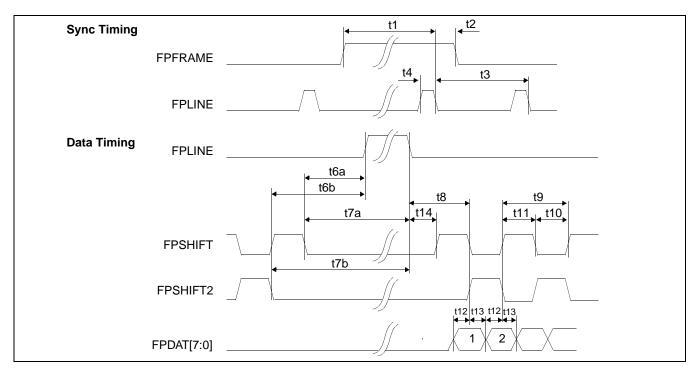

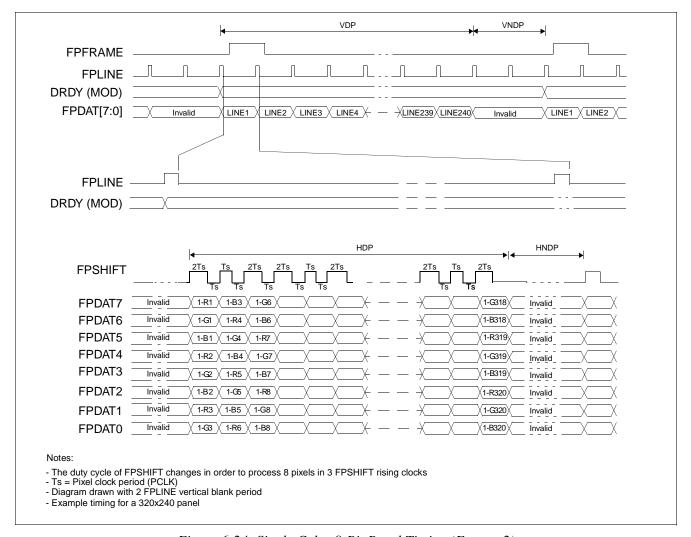

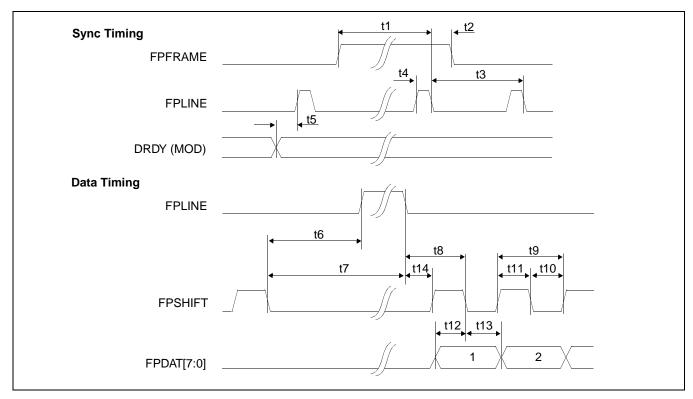

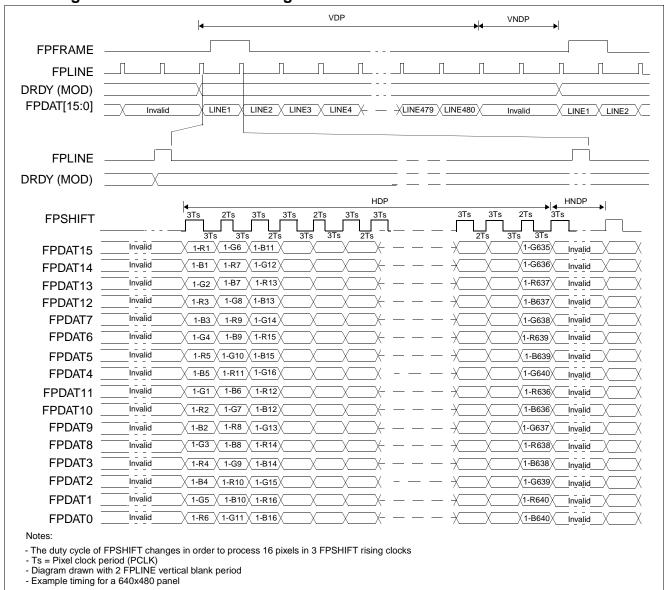

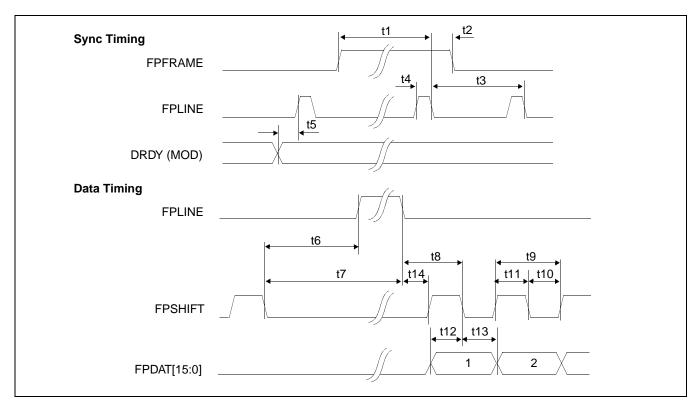

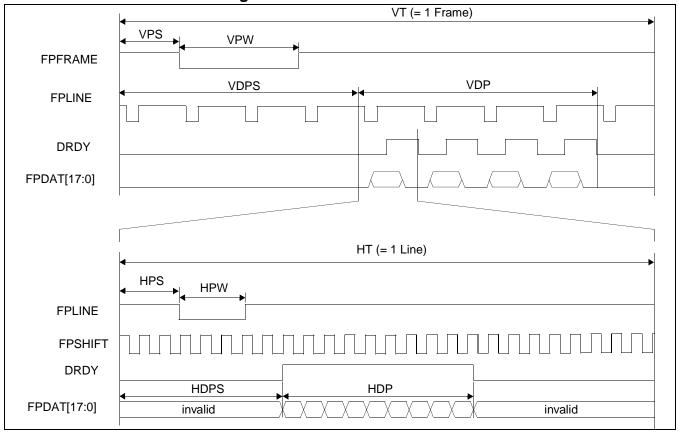

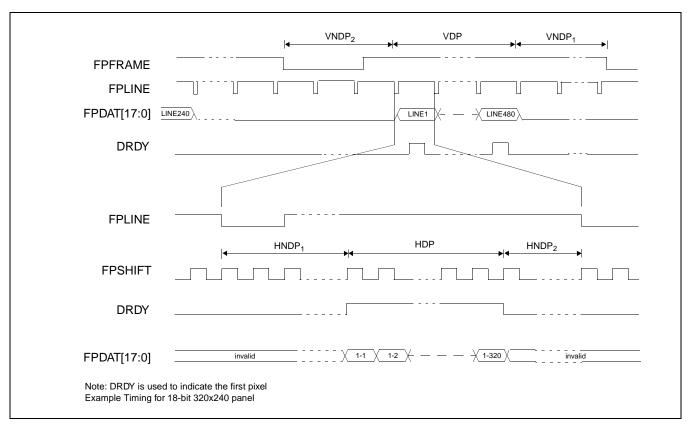

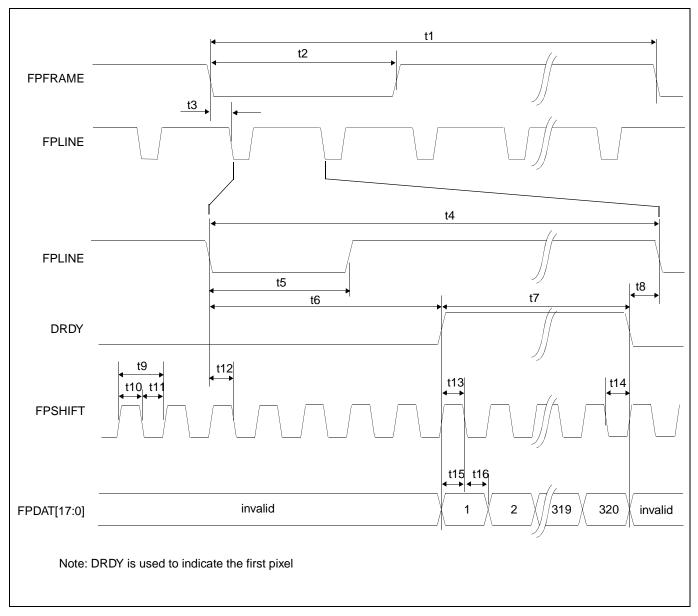

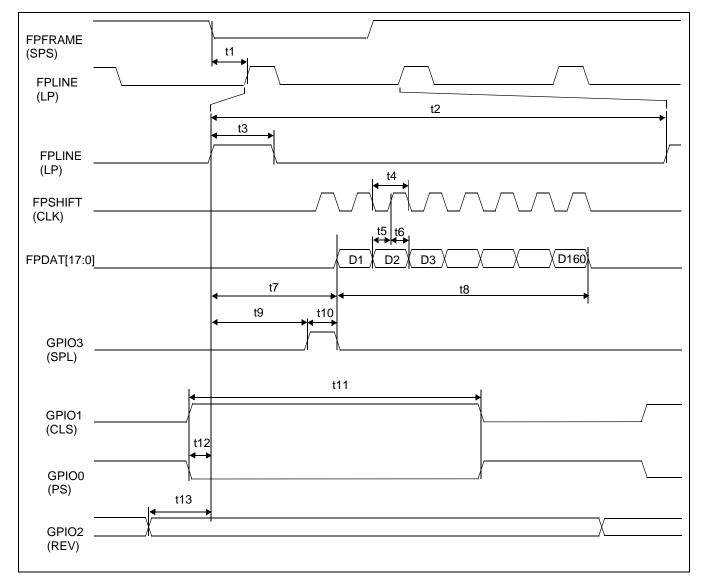

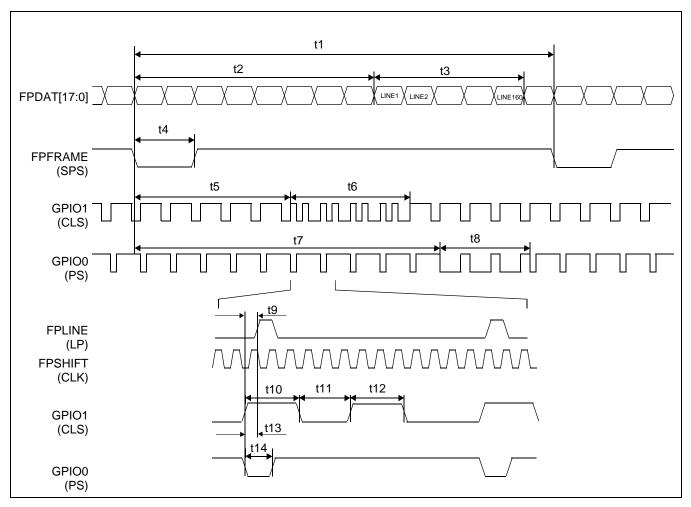

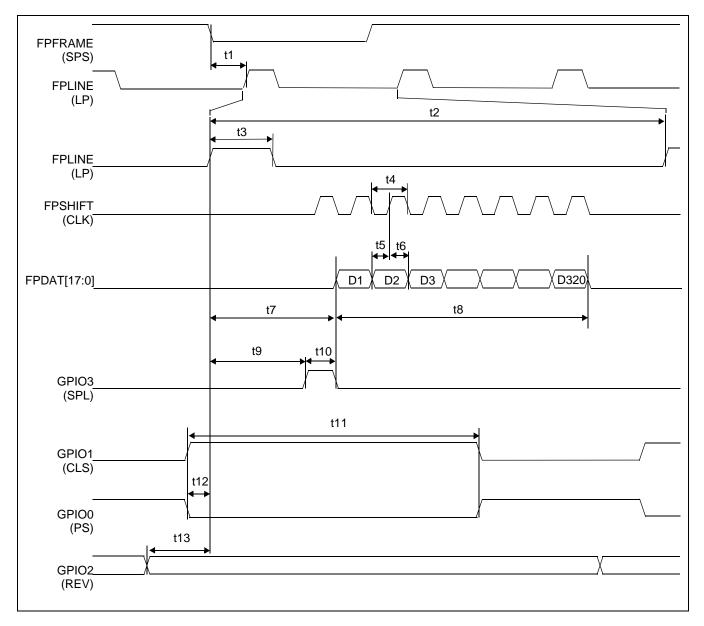

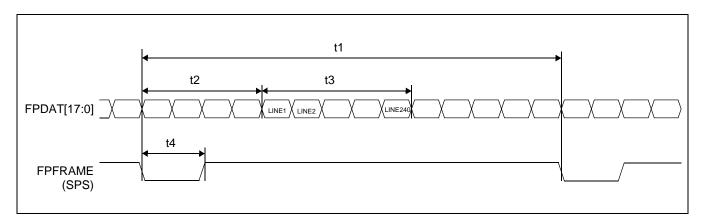

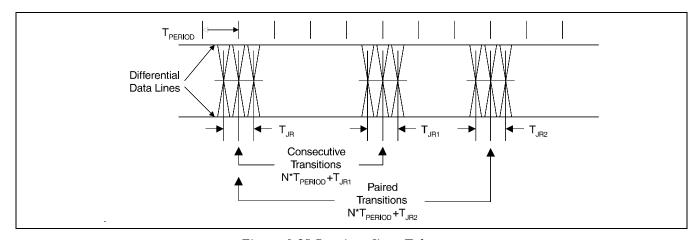

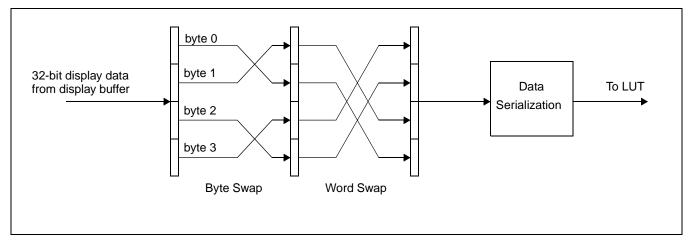

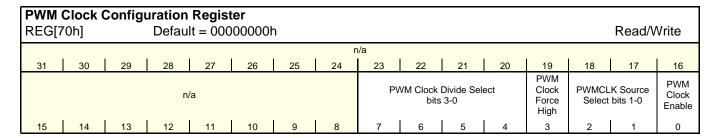

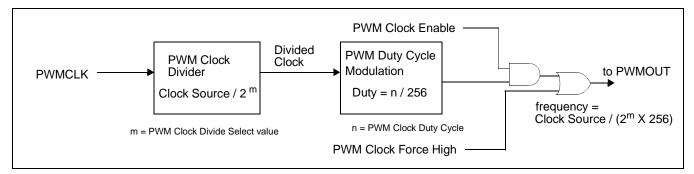

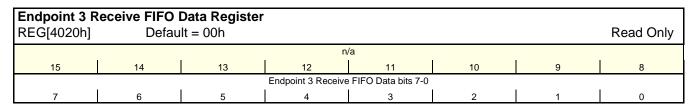

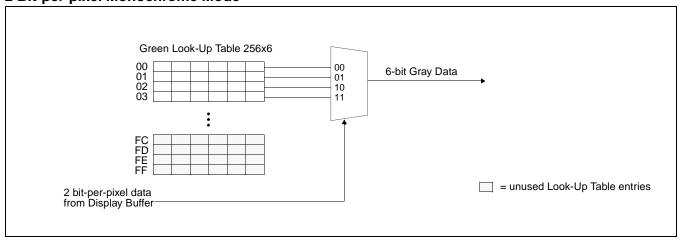

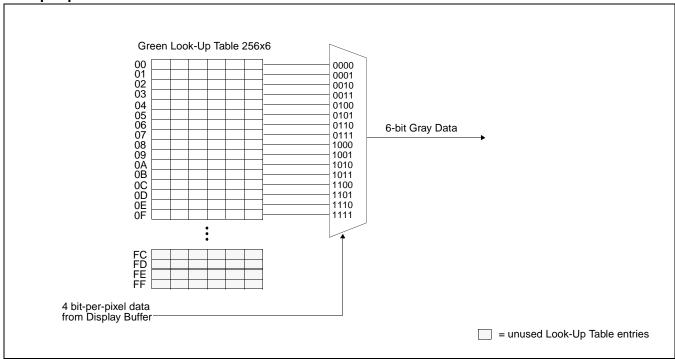

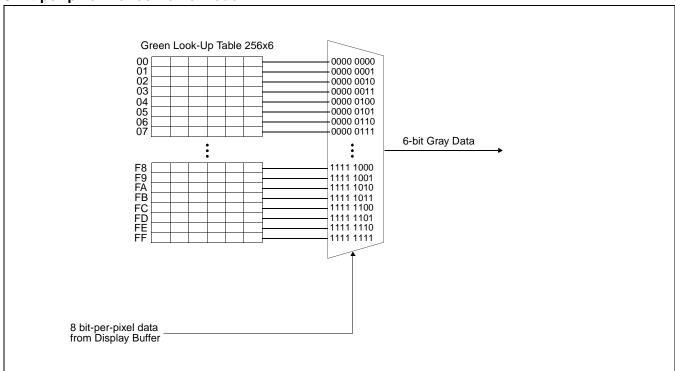

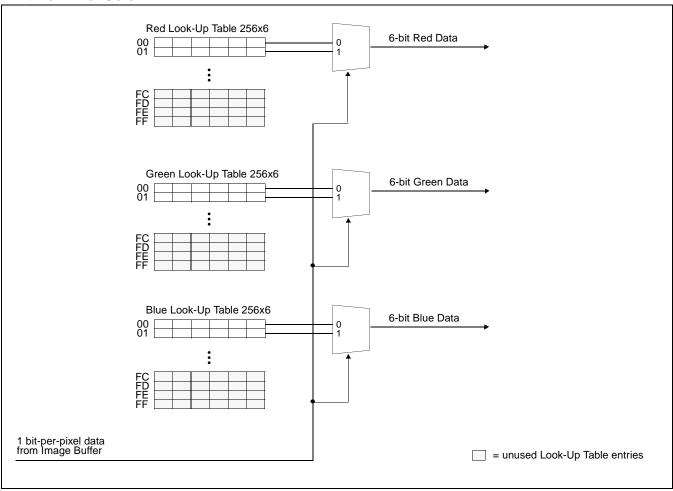

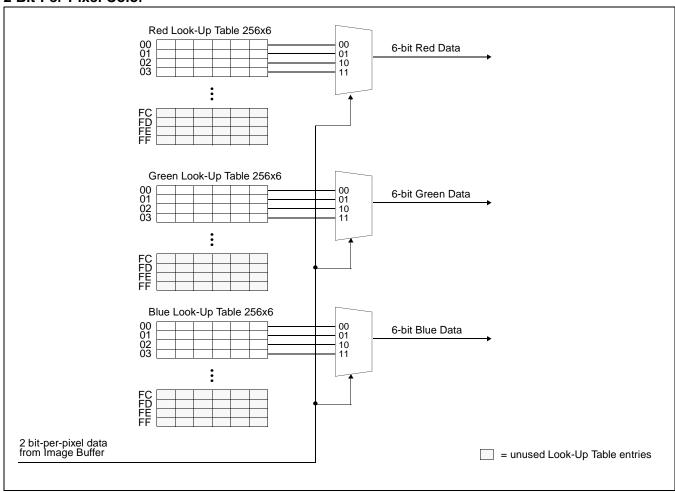

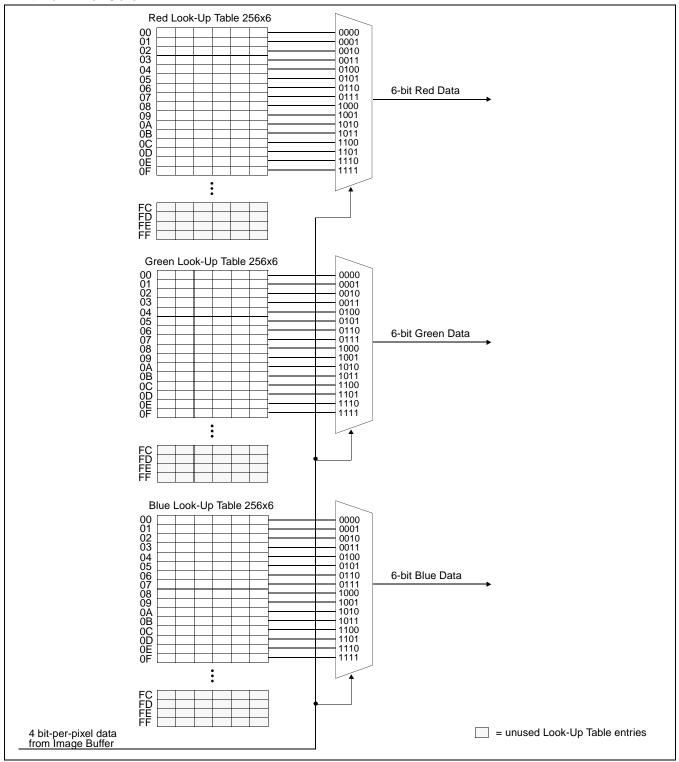

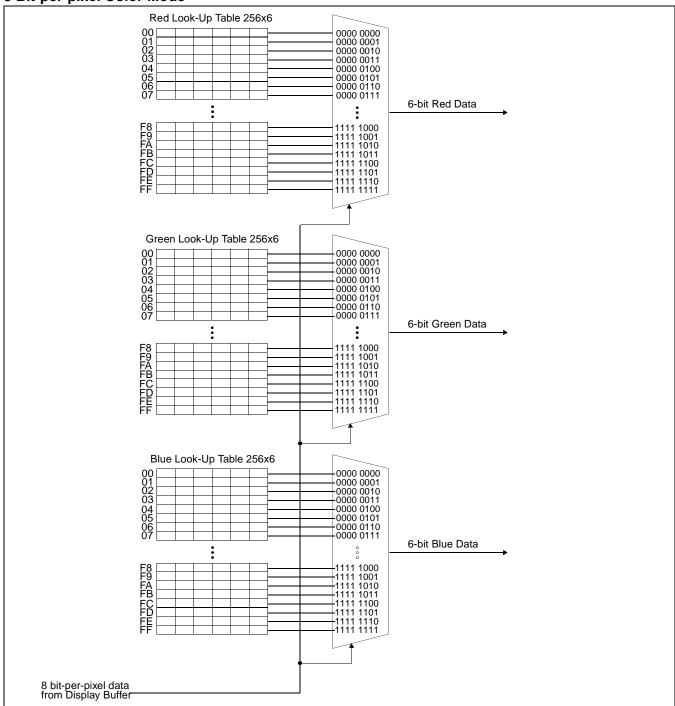

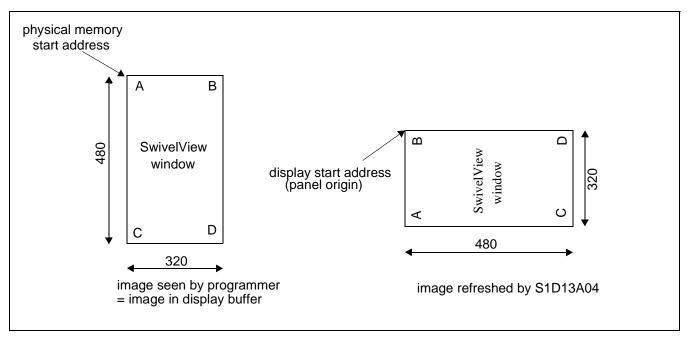

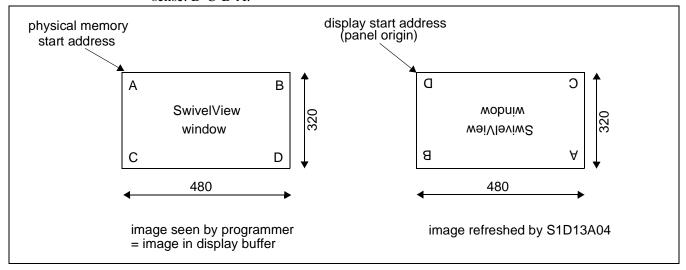

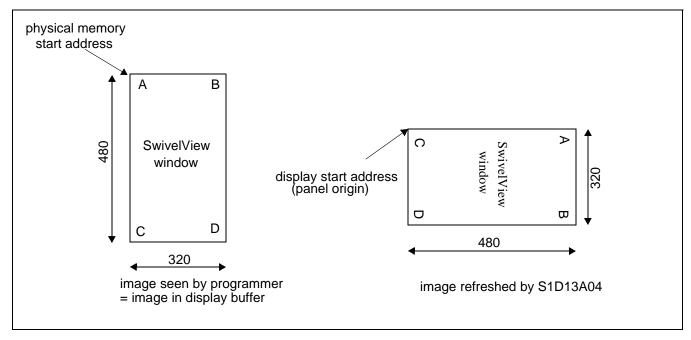

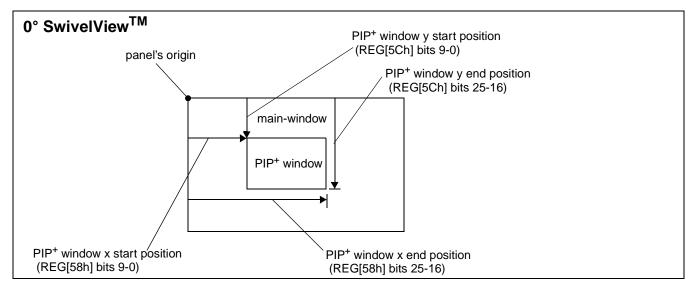

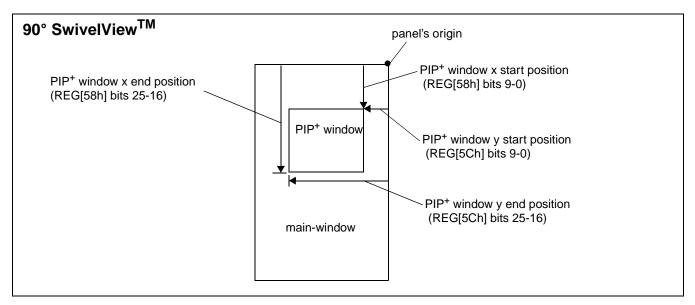

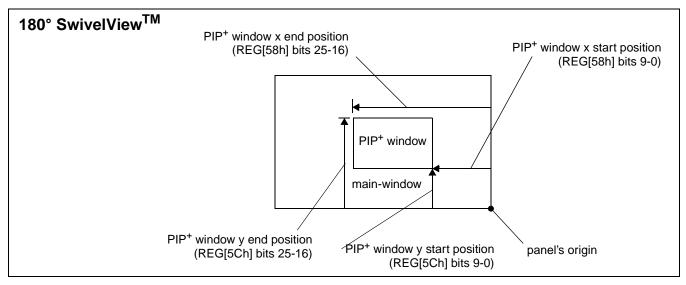

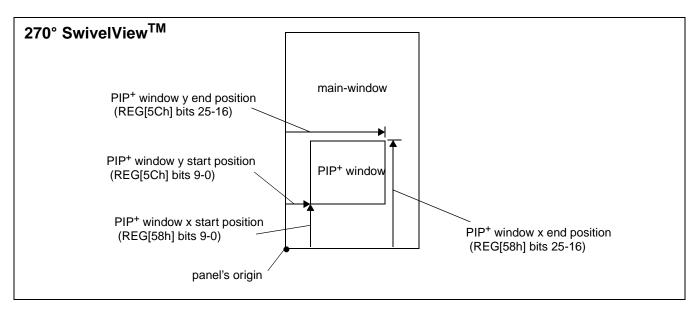

| FPDAT13  | driven 0         | driven 0         | driven 0             | driven 0             | driven 0             | D13 (G2) <sup>3</sup> | driven 0 | driven 0 | G1       | G1                  |